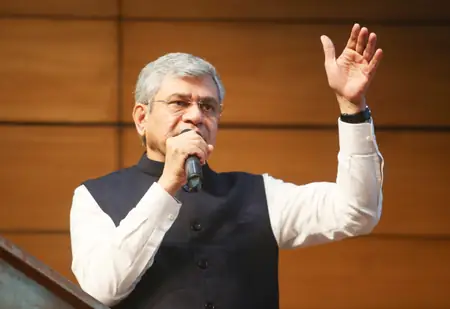

Union Minister for Electronics and IT, Ashwini Vaishnaw, shared exciting updates on India’s semiconductor push during a recent address. The ‘Chips to Startups’ program under ISM is hurtling towards training 85,000 design engineers at breakneck speed.

With a sharp focus on nurturing talent, the government has integrated advanced skill-building into the national agenda. The 10-year C2S initiative has shown impressive results within its initial four years, setting a strong foundation for India’s chip ecosystem.

Access to cutting-edge EDA tools from industry leaders—Synopsys, Cadence, Siemens, Renesas, Ansys, and AMD—has been granted to 315 educational hubs nationwide. Students are diving into real-world chip design, gaining invaluable hands-on experience.

The SCL in Mohali serves as the nerve center, where student-designed chips undergo fabrication, packaging, and rigorous testing. This holistic approach ensures graduates are industry-ready from day one.

Now the globe’s premier open-access EDA program, C2S boasts over 1.85 crore hours of tool utilization. Participation spans the length and breadth of India, from northeastern states to southern tech corridors.

Vaishnaw painted a bullish picture of the sector’s future: a market ballooning to $2 trillion, creating 2 million jobs globally. India’s young demographic stands to benefit immensely.

Announcing ISM 2.0, the minister revealed plans to scale up to 500 institutions. This expansion will supercharge talent pools in every facet of semiconductor manufacturing, cementing India’s strategic edge in the global supply chain.